Evolutionary optimisation of a morphological image processor for embedded systems

Edge autonomy lives and dies by milliseconds and milliwatts. This work showcases a two-pronged hardware strategy for embedded systems—particularly mobile robots—combining a high-speed morphological image coprocessor with a hardware genetic algorithm engine. Together, they aim to deliver faster perception, leaner implementations, and tighter integration than general-purpose compute can provide at the edge.

Why morphology matters at the edge

Morphological image processing—operations such as dilation, erosion, opening, and closing—excels at tasks like noise suppression, shape analysis, and segmentation. These operations are especially valuable in robotics and machine vision where decisions must be made from imperfect sensor data in real time. Yet, when implemented naively, morphology is compute- and memory-intensive, which is an ill fit for embedded platforms with strict power and latency budgets.

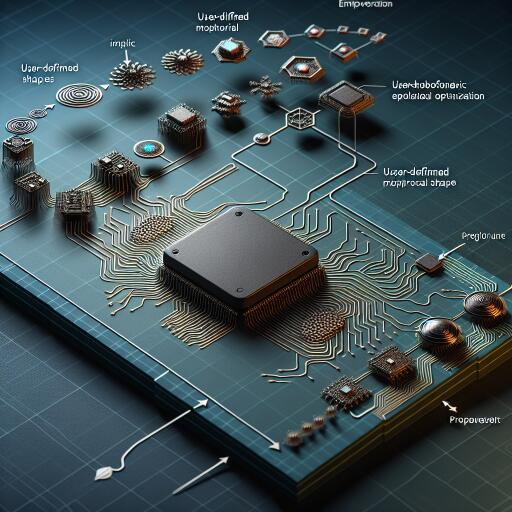

Inside the Clutter-II coprocessor

The first component, the Clutter-II, is a morphological image coprocessor purpose-built for speed, efficiency, and seamless system integration. Its architectural hallmark is a compact hardware structure for neighborhood transformations—the core primitive behind most morphological filters. By compressing the logic required to handle these local operations, the design significantly reduces hardware resource cost.

Fewer resources used per transformation directly translate into more parallelism: the saved gates and memory can be reinvested to instantiate additional processing lanes. This parallel scaling boosts throughput without inflating power or area beyond embedded constraints.

Integration is handled like a first-class citizen. The Clutter-II is designed as a coprocessor with clear, efficient access from the host CPU and application software. High-speed input/output interfaces, with separate instruction and data buses, streamline communication and decouple control from data flow. The result is a clean programming model and predictable latency—key attributes for time-sensitive robotic workloads.

Automating filter design with evolutionary search

Real-world pipelines rarely rely on a single primitive; they chain multiple morphological operations into filters tuned for a task. The thesis tackles the challenge of building such filters efficiently on the Clutter-II by introducing a genetic algorithm (GA) that searches for minimal-operation implementations. Instead of hand-crafting or over-provisioning, the GA evolves sequences that reproduce the desired filter while minimizing the number of operations—reducing both latency and energy per frame.

Crucially, the GA is tailored to the coprocessor’s compact transformation structure, ensuring that the evolved solutions map neatly to the available hardware primitives. This co-design approach—optimization guided by the actual hardware capabilities—maximizes the benefit of the compact architecture and yields practical, deployable filters.

From algorithm to silicon: the HERPUC GA processor

Experience gained from using evolutionary search to optimize image filters directly inspired the second component: the Hardware Evolutionary Reproduction and Processing Unit for Coprocessors (HERPUC), a hardware-based genetic algorithm engine. HERPUC implements a novel selection mechanism in hardware and pairs it with a flexible recombination operator. This design makes the evolutionary loop faster and more adaptable than conventional hardware GA implementations.

Why does that matter? In embedded scenarios, the costliest step in a GA is often the repeated evaluation of candidates. By improving selection efficiency and recombination flexibility, HERPUC reduces the number of fitness evaluations needed and effectively works with smaller populations—important for keeping memory, bandwidth, and power in check. The reported results show HERPUC solving its test problems with fewer evaluations and smaller populations than earlier hardware GA designs.

Performance and practical implications

- Resource efficiency: The Clutter-II’s compact neighborhood transformation structure cuts the hardware footprint per operation. The saved resources can be spent on parallelism, yielding significant speedups without abandoning embedded form factors.

- System-level throughput: Separate instruction and data buses and high-speed I/O make the coprocessor easy to drive from the host and easier to pipeline with sensors and downstream modules.

- Algorithm–hardware co-design: The GA-driven filter synthesis aligns software-level goals (fewer operations) with silicon realities, producing filters that are both accurate and fast on the target hardware.

- Evolution, accelerated: HERPUC’s hardware selection and flexible recombination enable solving optimization problems using fewer fitness evaluations and smaller populations than previous hardware GAs, shrinking compute and energy budgets.

What this means for embedded AI and robotics

For autonomous systems—drones, mobile robots, industrial inspectors—the synergy between a specialized vision coprocessor and an on-chip evolutionary engine is compelling. The coprocessor handles the heavy lifting of image morphology at wire speed; the GA engine adapts filters and solutions to new environments or tasks without round-tripping to the cloud. Together, they promise reduced latency, improved robustness to noise and clutter, and greater autonomy within tight power envelopes.

The bottom line

- Clutter-II delivers high-speed morphological processing through a compact, parallelizable hardware architecture and clean coprocessor interfaces.

- A bespoke genetic algorithm automatically derives efficient filter implementations by minimizing operation counts on the actual hardware primitives.

- HERPUC brings evolutionary computation into silicon, using a novel selection mechanism and flexible recombination to cut down fitness evaluations and population size versus prior hardware GA approaches.

In an era where edge devices must see, decide, and act within milliseconds, this pairing of morphological acceleration and evolutionary optimization points to a pragmatic path: design lean hardware, then use evolution to make it even leaner.